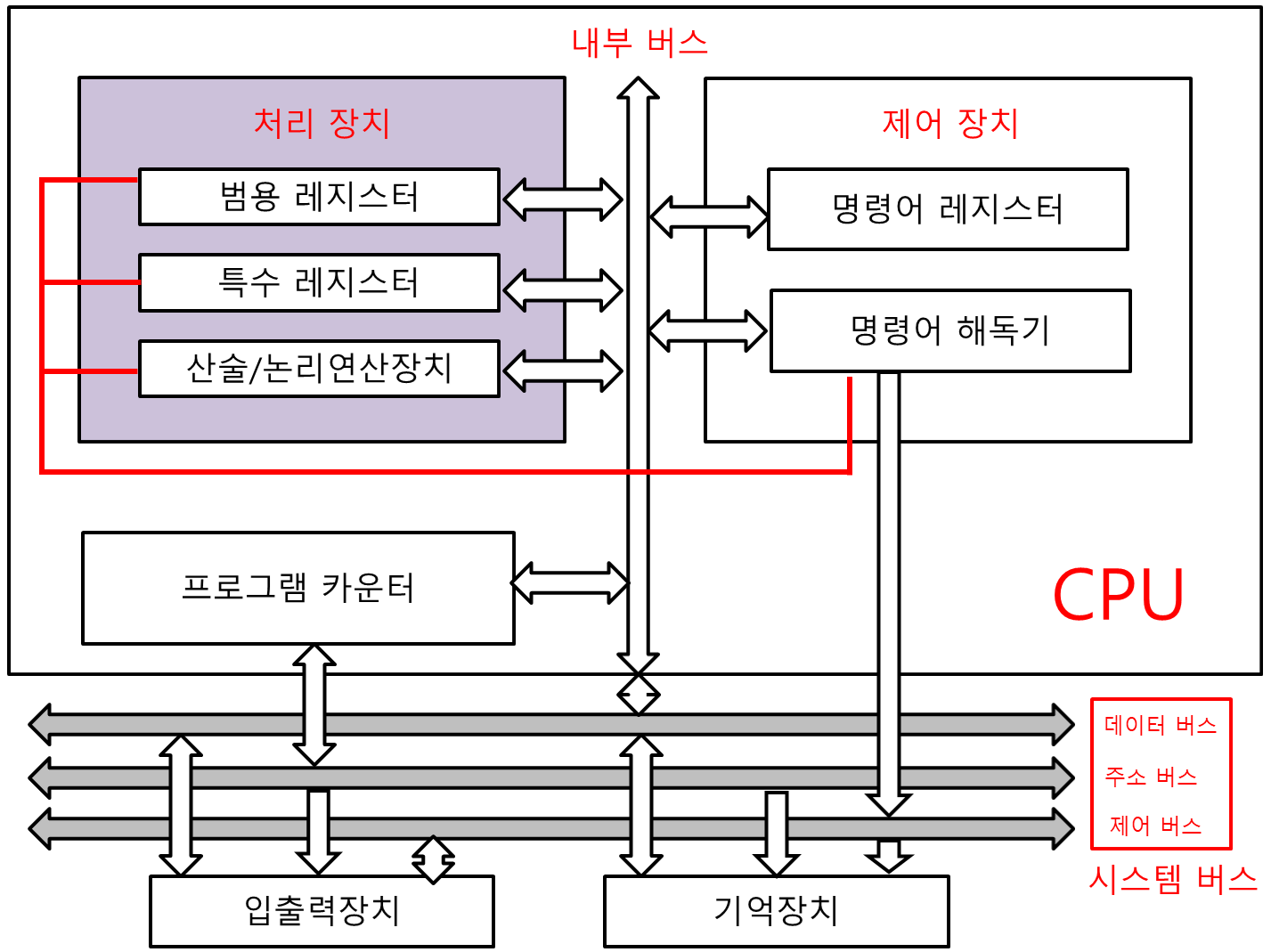

처리장치

처리장치는 산술/논리연산장치(ALU)와 레지스터, 내부버스로 구성되어있다.

산술/논리연산장치

산술연산, 논리연산, 비트 연산등의 연산을 수행하는 기능을 갖고 있다.

레지스터

연산에 사용되는 데이터를 저장하거나 연산의 결과를 저장하는 데 사용된다. 레지스터에 저장되어 있는 데이터에 대해서 실행하는 기본적인 연산을 마이크로 연산이라고 한다.

마이크로 연산

레지스터나 기억장치에 저장되어 있는 데이터에 대해 이루어지는 연산이다.

마이크로 연산은 전송, 산술, 논리, 시프트 이렇게 4가지 형태로 나누어진다.

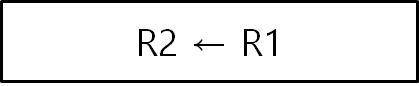

1. 전송 마이크로 연산

한 레지스터에서 다른 레지스터로 2진 데이터를 전송하는 연산

레지스터를 많이 가지고 있으면 프로그램의 수행에 필요한 데이터를 레지스터에 많이 저장할 수 있으므로 주기억장치의 접근 횟수를 줄여 프로그램의 실행속도를 높일 수 있다.

가. 표기식

- 레지스터 R1의 내용이 레지스터 R2로 전송됨을 나타낸다.

- 여기서 R1을 출발 레지스터라고 하고, R2를 도착 레지스터라고 한다.

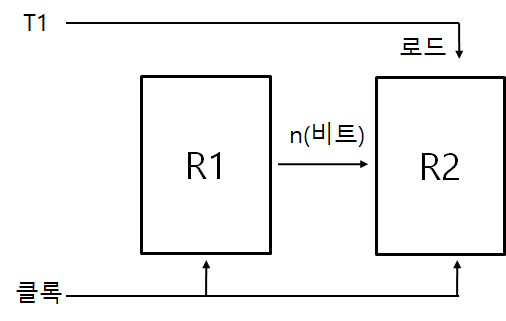

- 이러한 전송은 클록 펄스가 발생할 때마다 실행되지 않고 특정한 제어신호가 가해질 때만 실행된다.

- 레지스터 전송이 가능하기 위해서는 출발 레지스터의 출력과 도착 레시지스터의 입력이 회로로 연결되어 있어야 하며, 병렬로드의 기능도 포함되어야 한다.

* 병렬로드: 주고받는 레지스터의 모든 비트가 한 클록신호동안 동시에 전송되는 기능

- 조건문을 사용해서 표현이 가능하다.

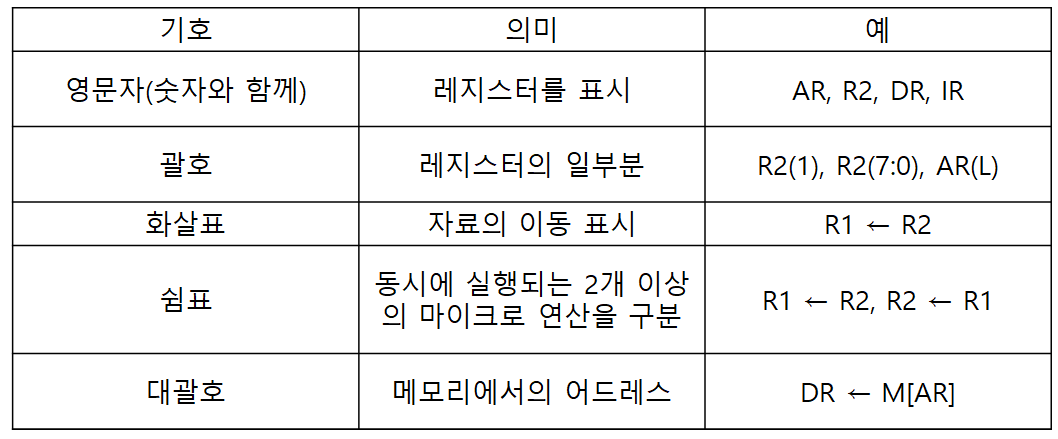

나. 레지스터 전송문장에서 사용하는 기본기호

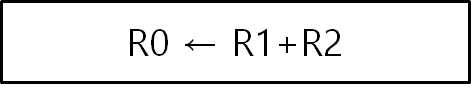

2. 산술 마이크로연산

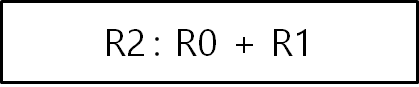

가. 표기식

기본적인 산술연산으로는 덧셈과 뺄셈을 포함하여 1 증가, 1 감소, 그리고 보수연산이 포함된다.

- 레지스터 R0에 있는 대뇽이 R1에 있는 내용과 더해져서 그 합이 레지스터 R2로 이동되는 것을 표시하는 문장이다.

- 뺄셈은 보수연산과 가산으로 구성하는 것이 일반적인다.

- 곱셉은 '*' 표기법을 사용하고 나눗셈은 '/'를 사용한다.

3. 논리 마이크로 연산

레지스터에 저장되어 있는 데이터의 비트를 조작하는 데 유용한 연산이다. 여기서는 각 비트를 독립된 2진값으로 취급한다.

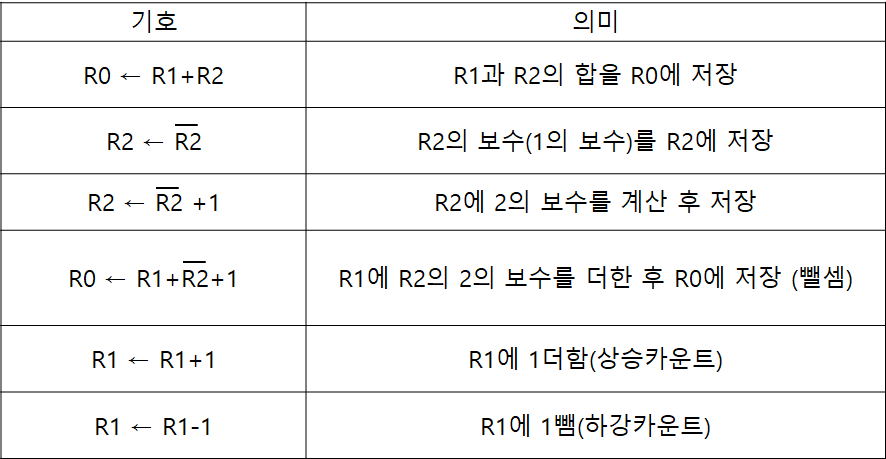

가. 표기식

- R1에는 1010이 들어있고, R2에는 1100이 들어 있다고 가정한다면, XOR 마이크로 연산은 위의 그림과 같이 논리 계산을 수행한다.

- 계산 수행 후 레지스터 R1에는 레지스터 R1과 R2의 각 비트들을 XOR연산한 결과가 저장된다.

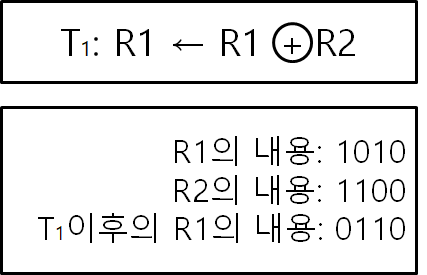

나. 논리 마이크로 연산에서 사용하는 기본기호

- NOT 논리연산은 모든 비트를 반전시켜서 1의 보수를 만드는 것과 동일하다.

- ∧ 기호는 AND 논리연산을 나타낸다.

- ∨ 기호는 OR 논리연산을 나타낸다.

- XOR 논리연산은 R1의 비트와 R2의 비트를 더한 결과를 R0에 저장한다. ( 1+1 = 0 )

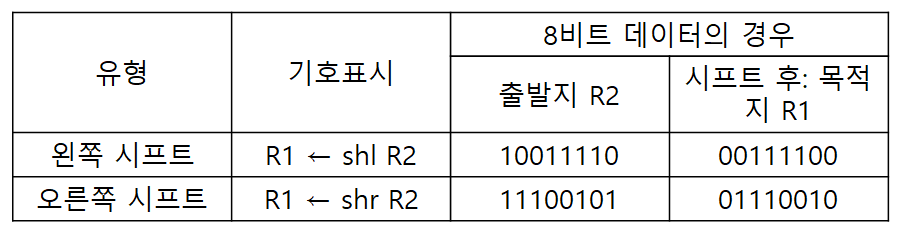

4. 시프트 마이크로 연산

데이터의 측면이동에 사용된다. 이 방식은 산술연산이나 논리연산, 제어과정에서 레지스터 내용을 변경하는 데 사용할 수 있다.예를 들어 출발 레지스터에 있는 내용은 왼쪽 혹은 오른쪽으로 시프트될 수 있다.

왼쪽으로 시프트: 최상위 비트의 방향으로 움직이는 것

오른쪽으로 시프트: 최하위 비트의 방향으로 움직이는 것

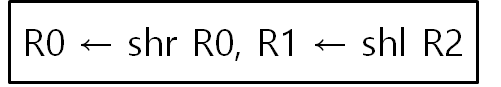

가. 표기식

- R0 ← shr R0는 레지스터 R0의 내용을 오른쪽으로 한 비트씩 시프트하는 것을 나타낸다.

- R1 ← shl R2는 레지스터 R2의 내용을 왼쪽으로 한 비트씩 시프트하여 R1에 저장하는 것을 나타낸다. 여기서 주의할 점은 시프트 연산을 수행하더라도 R2의 값은 변하지 않는다.

나. 시프트 마이크로 연산 예시

- 왼쪽 시프트연산에 도착 레지스터의 오른쪽 끝에 있는 비트를 입력비트라고 한다.

- 오른쪽 시프트연산에 도착 레지스터의 왼쪽 끝에 있는 비트를 입력비트라고 한다.

- 입력비트는 시프트 유형에 따라서 다른 값을 가질 수 있다. 여기서는 입력비트를 0으로 가정한다.

- 출력비트는 왼쪽 시프트의 경우 출발 레지스터의 제일 왼쪽 비트를 말하고, 오른쪽은 제일 오른쪽 비트를 말한다.

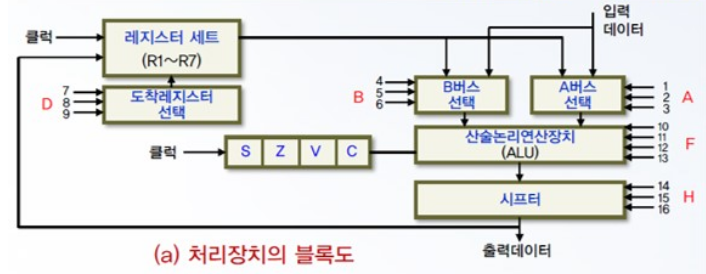

처리장치의 구성요소

1. 동작원리

가. 처리장치에 있는 각 레지스터는 ALU와 연결된 버스를 통해 2개의 멀티플렉서와 연결된다.

나. 각 멀티플렉서는 선택신호를 이용하여 특정 레지스터를 선택한다.

다. 2개의 멀티플렉서에 의해 선택된 데이터는 ALU에 의해 산술연산과 논리연산을 실행한다. 이때 ALU에서 연산결과에 대한 정보가 별도로 저장되는데 이를 상태비트라고 한다.

라. ALU에서 실행된 마이크로 연산의 결과는 시프트 레지스터를 거친다.

마. 시프트 레지스터를 통해 생성된 결과는 디코더가 선택신호에 따라 결정된 도착 레지스터에 결과가 저장된다.

* 처리장치에서 수행되는 각종 마이크로 연산은 선택신호에 의해 제어된다는 것을 알 수 있다.

2. 선택 신호에 따른 처리장치 동작 원리

가. 선택신호 A는 R1의 내용을 버스 A로 적재하기 위한 것이다.

나. 선택신호 B는 R2의 내용을 버스 B로 적재하기 위한 것이다.

다. 선택신호 F는 ALU에서 산술연산 A+B를 수행하기 위한 것이다.

라. 선택신호 H는 시프터에서 시프트 연산을 수행하기 위한 것이다.

마. 선택신호 D는 연산결과를 R0로 적재하기 위한 것이다.

* 선택신호들은 순서대로 발생되어야하며, 발생한 선택신호들은 처리장치의 각 구성요소를 제어하게 됨을 알 수 있다.

* 선택힌호들의 묶음을 제어단어라고 한다. 제어단어는 6번에서 자세하게 설명한다.

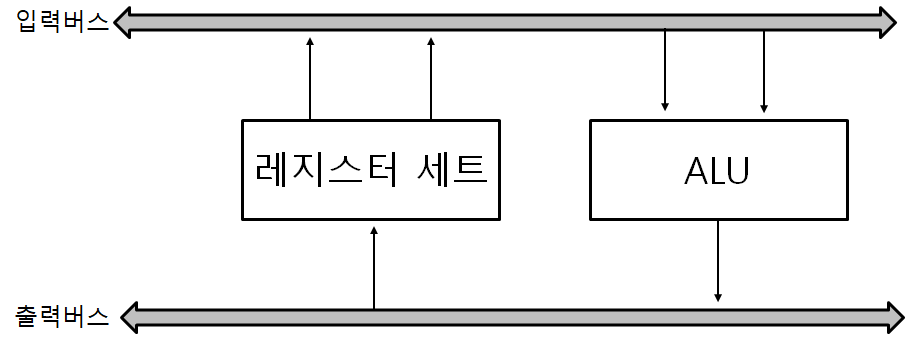

3. 내부버스

중앙처리장치 내부의 연산장치와 레지스터 사이의 정보 전송 경로를 말한다.

- 처리 장치 내부의 각 레지스터는 그 안에 저장된 정보를 입력버스를 통해 연산 장치로 전송하고, 연산장치에서의 연산결과는 출력버를 통해 통해 해당 목적지 레지스터로 전송된다.

- 멀티플렉서와 디코더를 이용하여 내부버스를 구성할 수 있는데, 멀티플렉서는 출발 레지스터를 선택하고, 디코더는 도착 레지스터를 선택하게 된다.

4. 상태비트

CPU의 제어장치가 다음 동작을 결정하는 데 사용되며, 상태비트가 저장되는 특수한 레지스터를 상태 레지스터라고 한다.

캐리(C): 산술연산에서 두 수를 가산할 때 캐리가 발생하면 bit가 1로 세트되고, 아니면 0이 된다.

오버플로(V): 산술연산에서 두 수를 가산할 때 결과를 저장 할 수 있는 레지스터의 자릿수가 모자라면 발생하는 에러이다. 오버플로가 발생하면 오버플로 비트가 1로 세트된다.

부호(S): 최상위 비트가 0이면 양수를 나타내고, 1이면 음수를 나타낸다.

제로(Z): 산술연산에서 두 수를 연산한 후 결과값이 0이면 1로 세트된다.

5. 시프터

시프트 연산을 수행하는 기능으로써 입력데이터의 모든 비트를 각각 서로 이웃한 비트로 자리를 옮기는 역할을 수행한다. 왼쪽시프트와 오른쪽 시프트가 있다.

* 시프트 연산은 앞에 시프트 마이크로 연산과 동일하므로 시프트 마이크로 연산을 참고하면 좋을 것 같다.

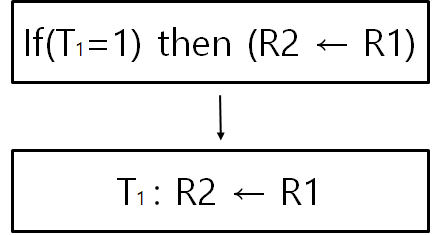

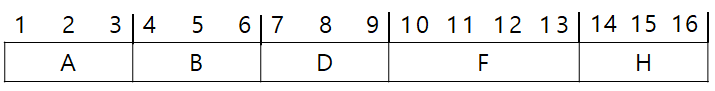

6. 제어단어

선택신호: 처리장치 내에서 수행되는 마이크로 연산을 선택하는 변수로서, 처리장치의 버스, ALU, 시프터, 도착레지서 등을 제어한다.

제어단어: 선택신호를 묶은 것을 제어단어라고 한다.

- 레지스터 세트는 R1~R7까지 7개의 레지스터로 구성되어있다.

- 7개의 레지스터 출력은 두 세트의 멀티플렉서가 선택되어 ALU의 입력으로 연결된다.

- ALU의 출력은 시프터를 통하여 출력버스로 연결되는데, 시프터로부터의 출력은 레지스터 중의 하나로 전송되거나 외부의 지정된 곳으로 전송될 수도 있다.

- 16개의 2진 선택신호가 있고, 이들을 묶어 제어단어를 구성한다.

A필드: ALU로 입력되는 A버스 선택(3비트)

B필드: ALU로 입력되는 B버스 선택(3비트)

F필드: ALU의 연산(4비트)

H필드: 시프터의 연산(3비트)

D필드: 도착 레지스터 선택(3비트)

결론

- 처리장치는 데이터를 처리하는 연산을 실행하는 것으로 ALU와 레지스터세트, 그리고 내부버스로 구성되어 있다.

- ALU는 산술연산, 논리연산, 비트연산, 수의 대소 판단 등의 연산을 처리하는 기능을 한다.

- 레지스터는 연산에 사용되는 데이터를 저장하거나 연산의 결과를 저장하는 데 사용된다.

- 마이크로연산은 레지스터에 저장되어 있는 데이터에 대해 실행하는 기본적인 연산으로 전송, 산술, 논리, 시프트 마이크로연산으로 나누어진다.

- 내부버스란 레지스터 간의 연결통로로 데이터 전송을 위한 공통선로의 집합이다. 내부버스는 멀티플렉서와 디코더를 이용하여 구성한다.

- 제어 단어는 처리장치 내에서 수행되는 마이크로연산을 제어하기 위해 구성요소의 선택신호를 묶어 놓은 것으로 여러 개의 필드로 구성될 수 있다.

- 제어 단어의 필드는 마이크로연산을 위한 출발 레지스터의 선택, ALU에서의 연산 선택, 시프터에서의 동작 선택, 결과가 저장될 도착 레지스터의 선택 등으로 구성된다.

< 참고자료 >

https://www.youtube.com/watch?v=EdTtGv9w2sA&list=PLBrGAFAIyf5rby7QylRc6JxU5lzQ9c4

[도서] 컴퓨터구조 - 김형근, 손진곤 지음 -

<Computer structures> chapter 12, 처리장치 end>

'CS(Computer science) > 컴퓨터 구조&운영체제' 카테고리의 다른 글

| 제어장치 (1) | 2024.07.03 |

|---|---|

| 파이프라이닝 (0) | 2024.06.30 |

| 중앙처리장치(CPU) (0) | 2024.06.30 |

| Deadlock (0) | 2020.02.15 |

| 프로세스 동기화 및 상호배제 (0) | 2020.02.02 |